想象这样一个场景:在一个干燥的冬日,你蜷缩在沙发上,穿着一双羊毛袜取暖。突然,门铃响了,你急忙走过一条地毯去开门。当你刚碰到金属门把手时,突然 “噼啪”一声。哎哟!起静电了。对于电子器件制造商来说,这种静电放电 (ESD) 现象可能会在工业应用中引发重大问题。这篇博客,我们将探讨如何借助建模和仿真避免这种问题。

静电放电器件损伤的类型

静电放电事件最常见且最明显的例子就是闪电,但并不是所有静电放电事件都会产生明显的火花。物体上积累的静电电荷量取决于其材料、表面积和周围环境的相对湿度。静电放电也可能由静电感应引起,当带电物体在远离地面的导电物体周围产生静电场时,就会发生静电放电。

图 1 有明显火花的静电放电事件。照片由 P. Mikołajek 拍摄,通过 Wikimedia Commons,遵循 Attribution-Sharealike 4.0 国际许可协议。

这些静电放电可释放几伏到几千伏的电压;然而,无论是简单二极管还是复杂集成电路电子元件,即使是低压放电也可能对电子元器件造成严重损伤。(一个人身上携带的电荷足以对电子器件和元件的性能造成损伤,从而导致数据丢失、文件损坏和系统崩溃!)因此,在这些器件的制造、组装和运输过程中,以及对于成品器件而言,预防静电放电事件都非常重要。

理解和预防静电损伤

为避免静电放电事件对电子器件和系统造成损伤,必须对元件、印刷电路板和系统各个层面进行各种测试。然而,这些测试只能在元件或系统制造完成后才能提供帮助。COMSOL Multiphysics® 软件能够帮助工程师在设计阶段发现静电放电问题,同时还能提供有关电磁场分布的详细信息,从而准确测试。这些知识对于理解静电放电损伤发生的原因以及如何修复损伤至关重要。

静电放电事件可能导致芯片绝缘故障或逻辑错误。当本应处于低电平状态(0)的引脚在超过 1 ns 的时间内承受振幅高于 1.5 V 的电压,或在超过 5 ns 的时间内承受振幅高于 0.3 V 的电压时,就会发生逻辑错误,从而导致引脚错误地转入高电平状态(1)。

接下来,让我们来看看静电放电如何导致印刷电路板上的微芯片出现逻辑错误。

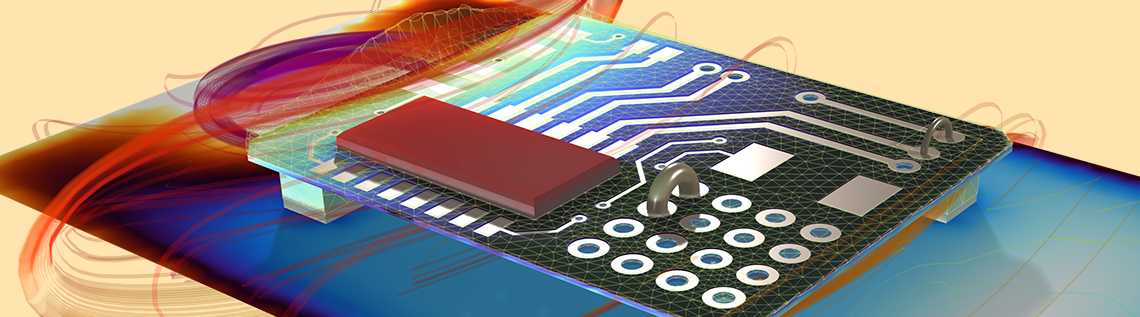

模拟电路板中的静电放电

RF 模块是 COMSOL Multiphysics® 的附加产品,包括用于静电放电电流研究的物理场接口。静电放电电流通常是非线性的,需要进行三维瞬态分析。电磁波、瞬态 接口包括四个预定义的静电放电电流,用于满足不同的测试标准,并支持预定义和参数化的时间脉冲函数,这些函数常用于描述静电放电和闪电。工程师可以在运行仿真前即刻绘制脉冲形状,以确保所选函数参数合适,方便检查。

在示例的模型中,静电放电电流是使用 集总端口 功能和扩展的人体模型(HBM)标准生成的,以测试极端条件下的性能(图2)。

请注意,我们不会在此介绍如何设置该模型的细节,欢迎点击文末链接下载此模型的 MPH 文件和相关说明。

仿真结果

模型计算了微芯片上两个引脚(1、2)的感应电压,以评估静电放电是否会导致误差。下图左侧显示了 t = 1.2 ns 时静电放电电流引起的表面电流密度,右侧显示了通过仿真计算的芯片的两个引脚(1、2)上的感应电压。

图 3 微芯片上两个引脚处的感应表面电流和电压。图中添加了一个虚拟的手指供参考。

可以看出,引脚 2 上的感应电压振幅高于 1.5 V,极有可能导致逻辑错误。

表面电流密度的模随时间变化,以对数刻度显示。

预防静电放电损伤的策略

静电放电是一种常见现象,也是导致电子器件损坏和故障的主要原因。随着器件尺寸的不断缩小和电路密度的持续增加,制造商越来越需要密切关注静电放电损伤的预防。

数值仿真提供了一种深入理解这些微型器件的方法,以及在需要建立物理原型之前准确模拟和优化设计的方法。它还可以作为一种预兼容测试,对各种测试进行有效补充。仿真测试的通过可以高度增强设计人员对物理实验的信心。仿真还可以帮助探究故障机理和电流分布,并提供有效的解决方案。

下一步

想尝试自己动手模拟文中示例的静电放电模型吗?您可从 COMSOL 案例库中下载包括分步说明在内的所有模型文件。

评论 (0)